TSV 공정: 1. via 형성 2. via 채우기 3.Thinning 4.본딩

1. via 형성

통상적으로 Bosch 방식의 DRIE(Deep Reactive Ion Etch) 방법을 사용

높은 종횡비의 via를 구현할 수 있으나 옆 벽의 표면이 균일 하지 못하다

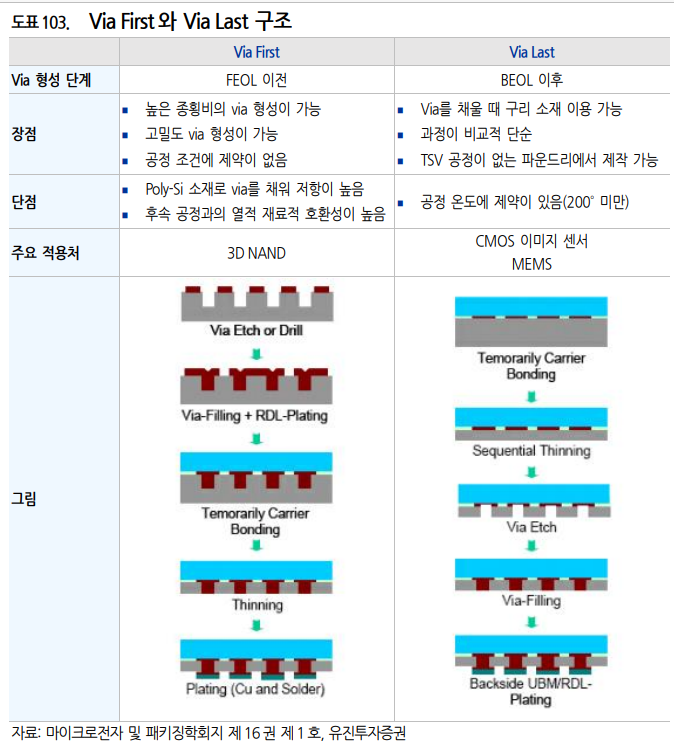

Via 를 어떤 단계에 형성하는지에 따라 Via First 구조와 Via Last 구조가 있다

2. via 채우기

Via 를 형성한 후에는 주변에 절연층을 추가하여 전기적으로 절연시키는 단계를 거친다.

이후 via 내부는 전자 신호가 오갈 수 있게 전도성 금속 물질을 채워 넣는다

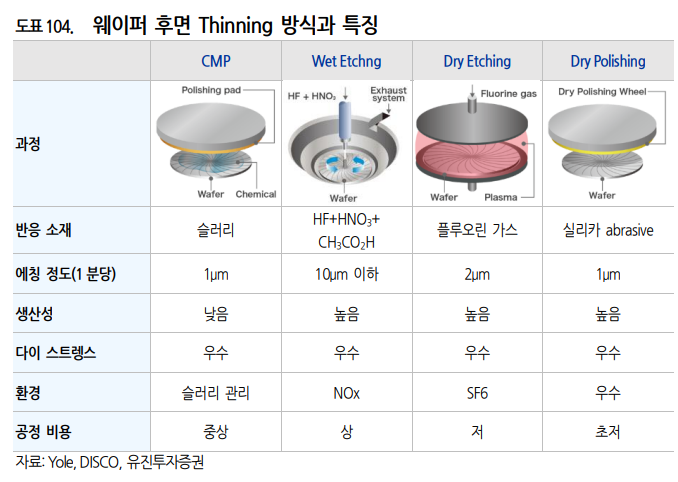

3.Thinning

다음으로 웨이퍼의 후면에서 특정 두께를 제거하여 via가 기판을 관통할 수 있게 해야 한다.

크게 그라인딩, CMP, 습식 에칭, 건식 에칭 방식이 있으며

그라인딩과 CMP/ 그라인딩과 습식/ 그라인딩과 건식 에칭 방법을 혼용

그라인더 장비의 경우 일본의 DISCO 와 ACCRETECH(동경정밀)이 시장을 주도하고 있고,

국내의 경우 비상장사인 이화다이아몬드 등의 기업에서 생산

웨이퍼 후면을 깎아낼 때 중요한 CMP 공정 장비는 케이씨텍, 비상장사인 엔티에스가 생산

건식 에처 장비는 압도적으로 Applied Materials 와 Lam Research 가 공급

4.본딩

얇아진 웨이퍼는 두께가 수십 μm 이하이기 때문에 특별한 핸들링이 필요한데,

이 때 투입되는 것이 웨이퍼 서포팅 캐리어이다.

유리판이나 캐리어 웨이퍼를 디바이스 웨이퍼에 임시로 붙여 이후 공정을 진행한다.

마지막으로 TSV 가 형성된 칩 또는 웨이퍼의 본딩 공정을 수행한다.

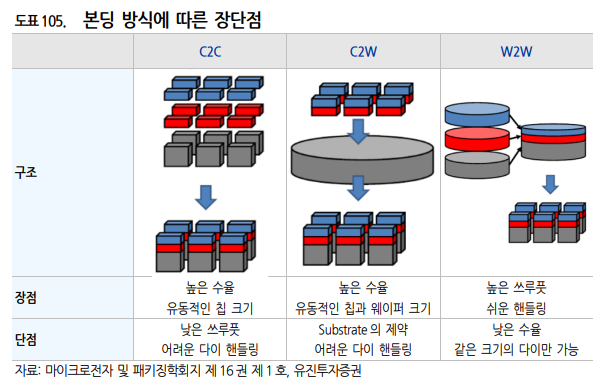

본딩 방식으로는 C2C(Chip to Chip), C2W(Chip to Wafer), W2W(Wafer to Wafer) 세 가지가 있으며 난이도는 W2W 가 가장 높다.