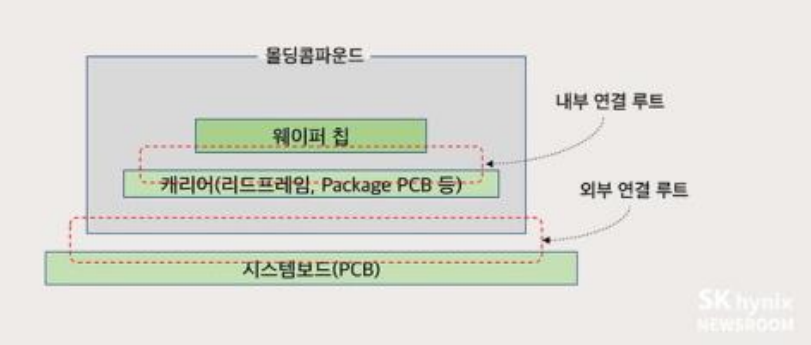

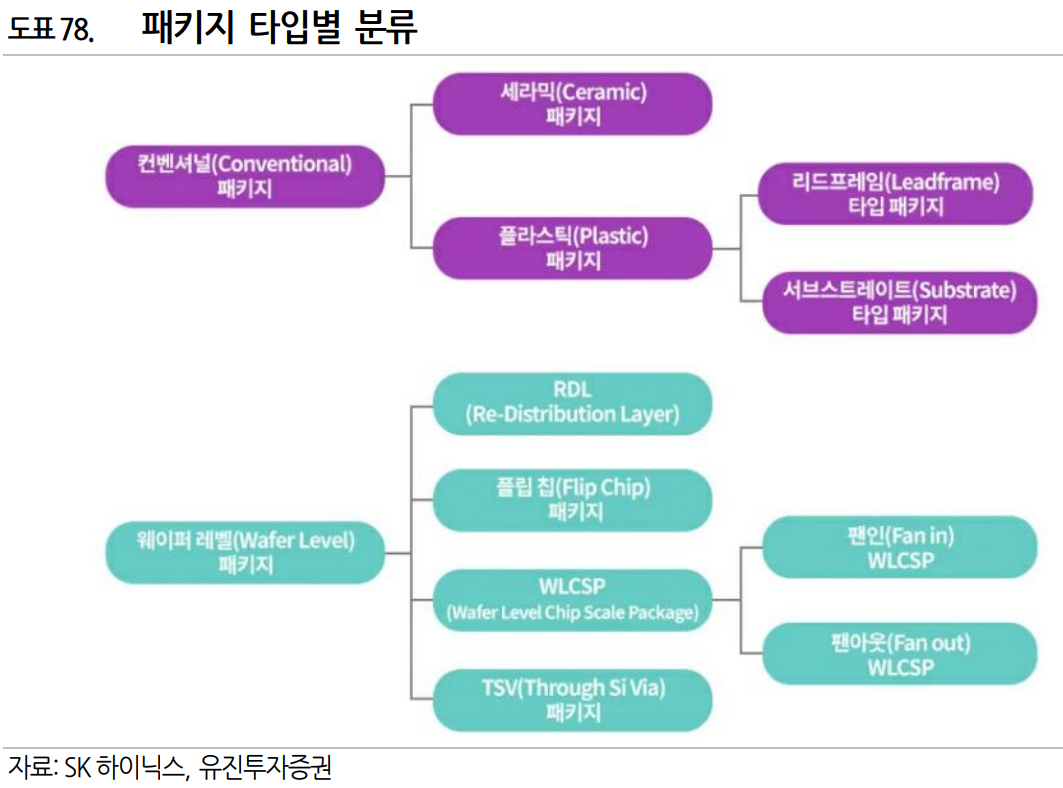

<패키지의 기본 구조>

웨이퍼에서 분리된 칩과 칩을 올려놓는 캐리어, 이 전체를 둘러싸고 있는 몰딩 컴파운드로 이루어져 있다.

내부의 칩과 외부를 연결하고 신호를 주고받을 수 있는 통로가 필요한데, 이 통로는 내부 연결과 외부 연결 루트로 불린다.

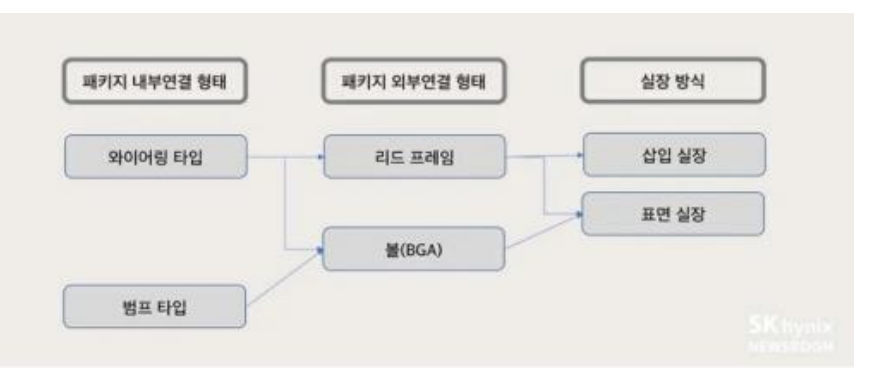

과거 와이어 본딩 과정에서는 1 차 연결 단자로 와이어, 2차 연결 단자로 리드프레임을 사용했다.

어드밴스드 패키징부터는 1차 연결 단자가 솔더 혹은 골드 범프, 2차 연결 단자는 솔더 볼이 활용된다.

실장 방식은 삽입 실장과 표면 실장으로 나뉜다.

< 패키지 내·외부 연결 형태와 실장 방식 >

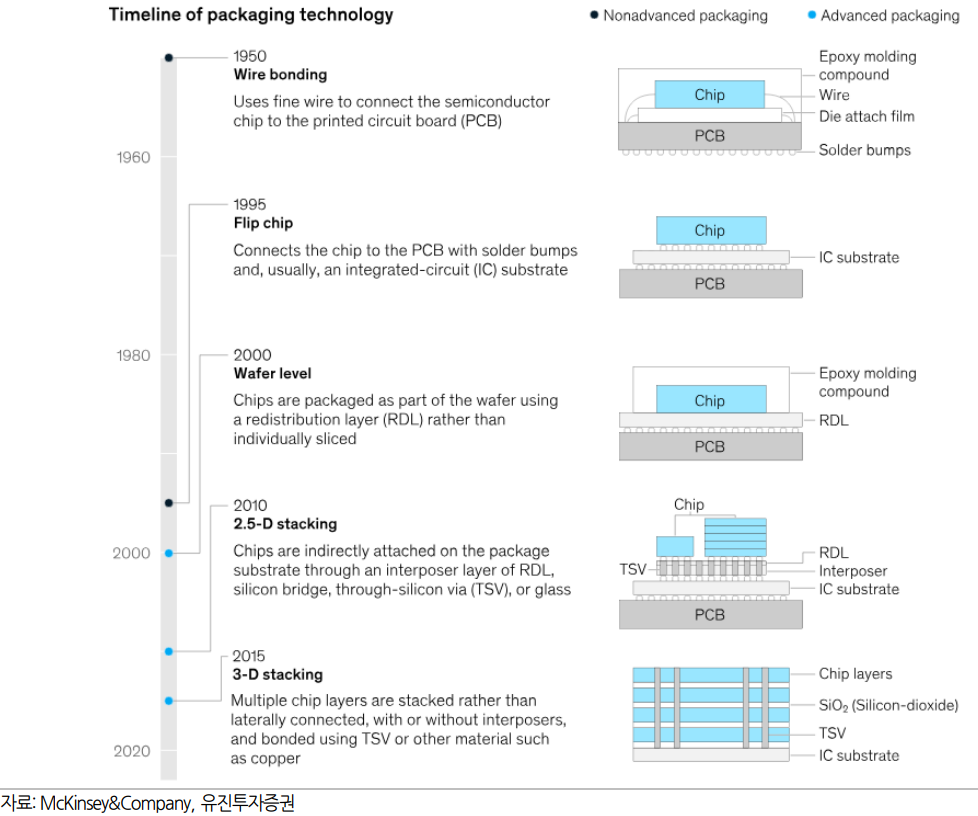

다이 투 다이로 진행되었던 패키징 산업의 영역이 웨이퍼 단으로 올라오면서 전공정 기술을 포함

어드밴스드 패키징을 통해 ‘Middle-end’라는 영역이 새로이 정의된 이유도 이 때문

< 패키징 기술 발전사 >

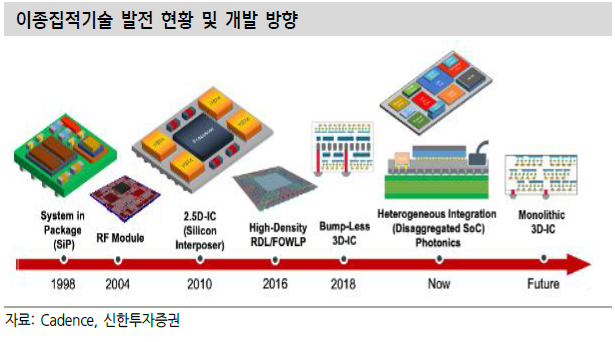

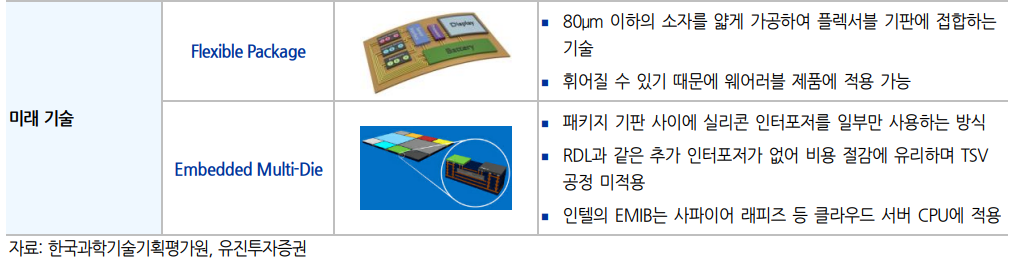

현재 반도체 패키지 기술 진화 방향성은 이종집적(Heterogenous Integration)기술이다.

이종집적기술은 로직 및 메모리 반도체 등 다양한 이종 반도체 소자들을 하나의 패키지 안에 구현하는 기술이다.

패키지 간에 전기적 신호를 주고받는 것보다 패키지 안에서 칩 간에 전기적 신호를 주고받을 수 있게 된다.

전기가 이동하는 거리가 짧아지면서 전기 저항이 줄어들어 전력 효율이 향상된다.

최근에 새롭게 개발된 기술은 아니다.

1970년대는 MCM(Multi-Chip Module), 1998년부터는 SiP(System in Package)로 구현되기도 했다.

현재 2.5D, Chiplet,TSV(Through Silicon Via) 등 다양한 기술을 접목하여, 독립적으로 생산된 여러개의 칩을 하나의 패키지에 조립하고 있다.

1) SiP(System in Package):

로직 칩과 메모리 칩을 하나의 패키지 안에 수평적으로 배열한 패키지 방식이다.

이종집적기술이 발전하며 2.5D, 3D, 3.5D 패키지 등 로직 칩과 메모리 칩을 하나의 패키지로 연결하는 기술이 개발됐다. 이는 발전된 형태의 SiP라고 생각해도 무방하다.

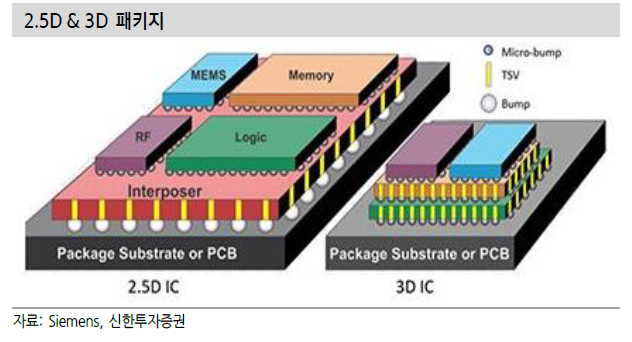

2) 2.5D Package:

로직 칩과 메모리 칩을 수평적으로 배열한 패키지 방식이다.

2.5D 패키지는 반도체 칩과 기판 사이에 인터포져(Interposer)라는 제2의 기판을 추가적으로 배치한다.

I/O 밀도 차이가 커진 칩과 기판 사이의 배선 연결을 돕기 위해서다.

인터포저는 중간 수준의 배선을 구현하여 칩과 기판 사이의 물리적인 연결을 구현하고, 전기적인 신호 전달을 용이하게 한다.

3) 3D Package:

로직과 메모리를 포함한 여러 기능의 칩을 얇게 쌓아 올리는 패키지 방식이다.

칩을 수평이 아닌 수직으로 배열 적층할 경우 면적을 최소화할 수 있고 전자의 이동거리는 더 짧아진다.

이에 전류 이동 속도를 향상시켜 데이터 전송 속도가 더 빨라진다.

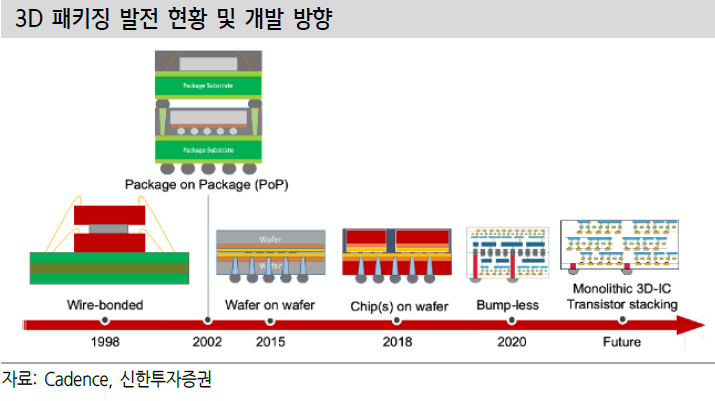

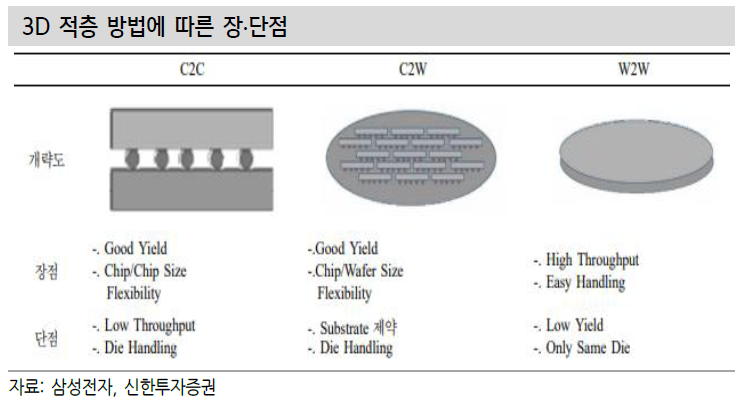

3D 적층 기술은 어플리케이션의 특성에 맞게 패키지와 패키지를, 또는 칩과 칩을 적층하는 방식으로 발전했다.

칩과 칩을 적층하는 방식에서도 칩과 웨이퍼(C2W), 웨이퍼와 웨이퍼(W2W) 방법 등 다양한 3D 패키지 기술이 개발됐다.

전기적 연결 통로를 만드는 본딩 공정은 기존에 내부 칩과 외부와의 전기적 통로를 만드는 역할을 했다.

하지만 3D 적층 기술이 개발되며 칩과 칩을 전기적으로 연결하는 기술도 함께 발전했다.

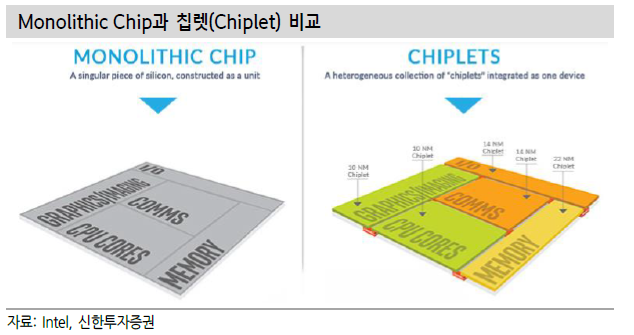

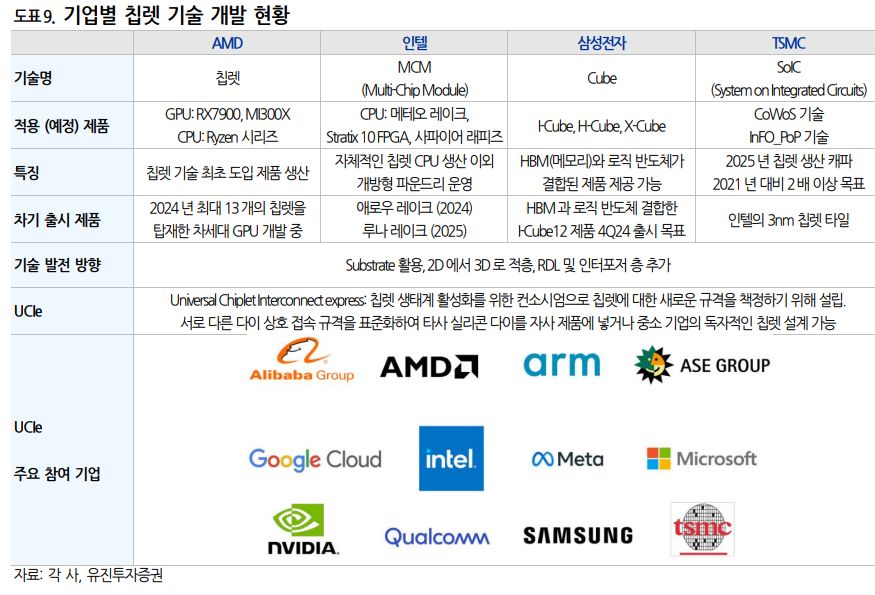

4) 칩렛(Chiplet):

기존에 한 개의 대형 단일칩(Monolithic)에 구현되는 반도체 소자들(연산 소자, 메모리 소자, RF 기능 등)을 독립적으로 생산하여 이종칩들을 연결하는 방식이다.

과거 반도체 크기의 소형화 및 성능 개선을 위해 한개의 반도체 위에 여러 시스템을 집적하는 SoC(System on Chip)가 주력을 이뤘다.

하지만 '1) 설계 난이도의 어려움, 2) 수율 악화’로 단일칩에 있는 기능을 별도의 칩으로 생산하여 연결하는 칩렛이 현재 주목을 받고 있다.

***과거 칩 간 상호 호환성을 높이고자 활용하는 기술에 표준이 없었다.

다이의 상호 접속 규격인 입출력 단자(I/O, Input/Output)가 달라 이를 표준화하기 위한 UCIe(Universal Chiplet Interconnect express)라는 컨소시엄이 설립

2023 년 8 월 1.1 버전을 발표해 범프 피치에 따른 인터커넥션 표준이 제시

이종접합(heterogeneous integration)은 TCB와 HB 장비 등 여러 가지 패키지 기술로 구성

HB와 TCB가 공존할 것으로 예상한다.